Crosstalk Jitter

This item checks the amount of signal jitter due to even/odd-mode crosstalk.

This item analyzes and checks odd-mode and even-mode crosstalk jitter of target nets.

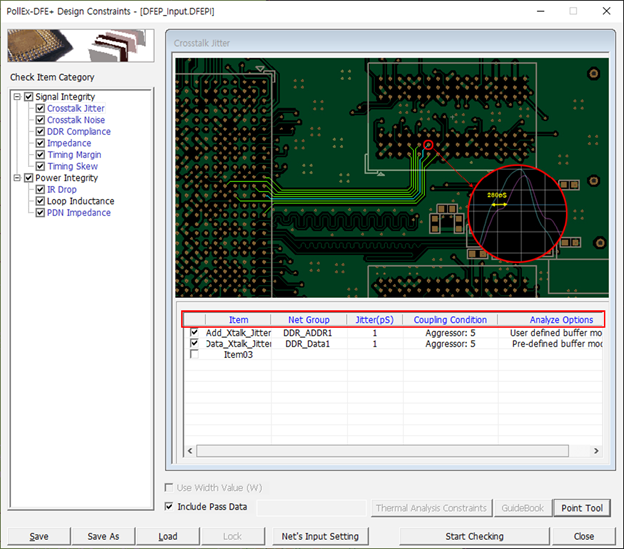

Figure 1. Crosstalk Jitter

- Item: Sub item name. You can enter arbitrary name.

- Net Group: Select target net groups to be tested. Allow multiple net groups.

- Jitter: Enter allowable maximum crosstalk jitter amount in pS unit.

- Coupling Condition: Change the following coupling conditions. number of coupling signal layers, number of traces to be coupled, coupling length, distance, and so on.

- Analyze Options: You can assign driver/receiver buffer simulation model, driving strength of driver and other simulation parameters. The default buffer model is initially assigned to the buffer model field which can be changed. When the device models are not available in the part data, the default linear device models defined here are used for transient simulation of signal integrity analyses.

- The region shows the names of all coupled nets. Total 7 aggressor nets listed together with the victim MCU_AA0 net.

- Display region shows detailed coupling topologies.

- Nets selected by checkbox of Aggressor Net are displayed in the image display area.

- Aggressor Net: Many fractal segments can be listed at this column coupled to the victim net.

- Separation: Aggressor net MCU_ABA2 can have different separations to the victim depending on the locations.

- Victim Layer: With Aggressor Layer, two columns show where the coupled traces, one is victim and the other is aggressor, are routed.

- Coupled Length: Shows the coupled length for the fractal coupled segments.

- Transient Analysis Parameters: Enter required analysis parameter.

- Simulation Time (ns): Enter end time of the SPICE transient analysis.

- Signaling Time (ns): Input Signal having pulse period will be excited to the net until the time assigned here.

- Preamble Time (ns): Simulation start after this time to wait until status of internal circuit becomes stable.

- Default Device Models: When the device models are not available in the part data, the default linear device models defined here are used for transient simulation of signal integrity analyses. With the use of Linear Device Modeler, you can create linear output (driver) and input (receiver) device models and store them in a linear device model file. PollEx DFE+ provides users with a system default linear device model file, UDVS.dmf.

- Active Driver Pins & Device Models: Click then Active Driver Pins & Device Models dialog is invoked. You can define whether the excitation signal is applied or not for each aggressor nets here. During crosstalk jitter analysis, the Active Driver Pin of victim net also set as drive. Just do the crosstalk analysis with all aggressor and victim nets are excited. You can change the Initial State, Pulse Period(ns) and Device Models by clicking these for the desired net.