Altair PollEx 2022.3 Release Notes

This section contains all the changes for the 2022.3 release for PollEx.

Highlights

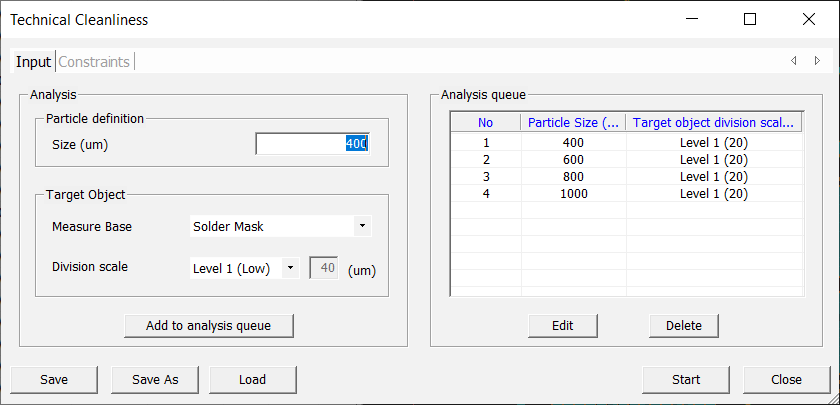

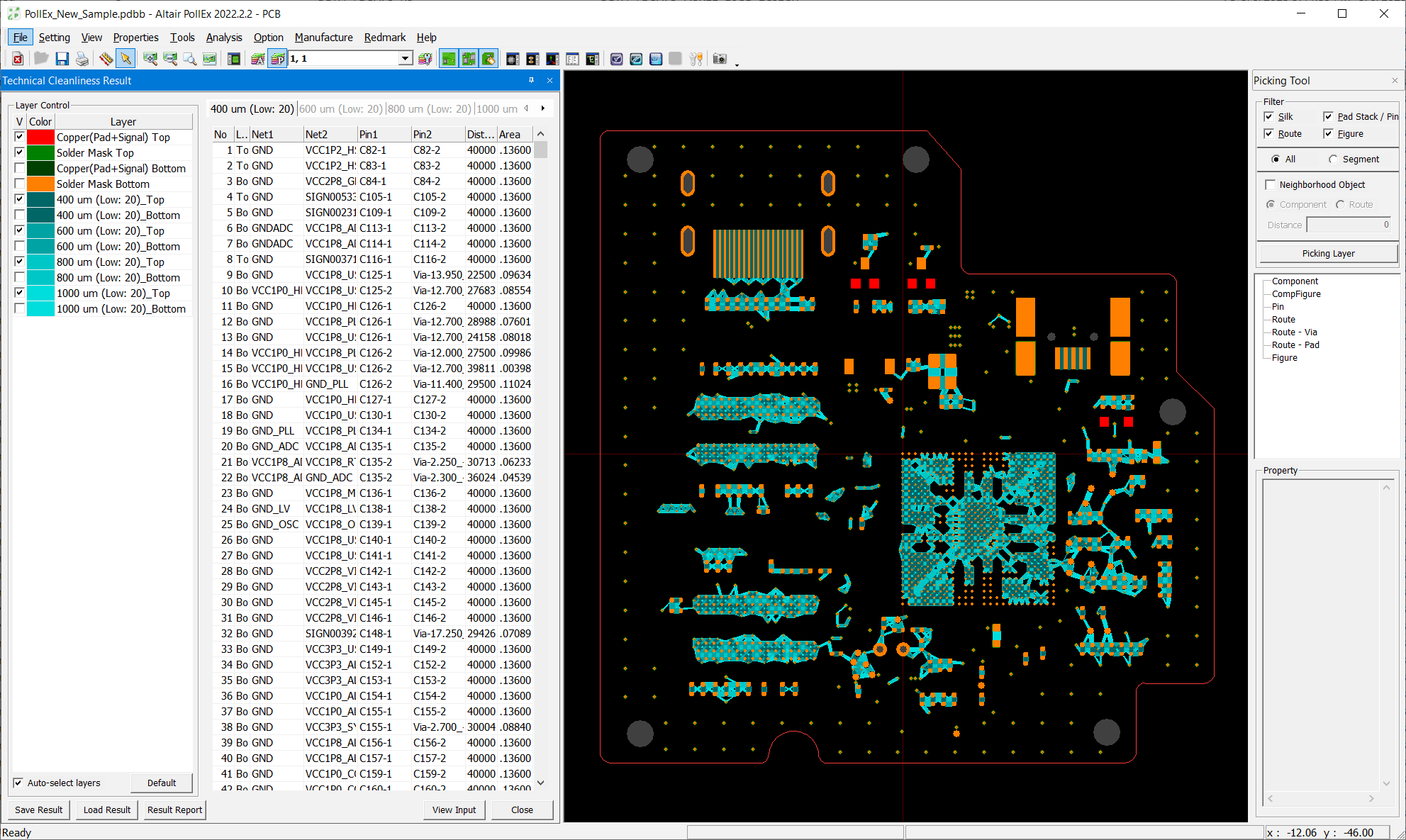

- Added a Technical Cleanliness menu to inspect and

analyze contamination and ensure cleanliness from particles on a PCB

board.

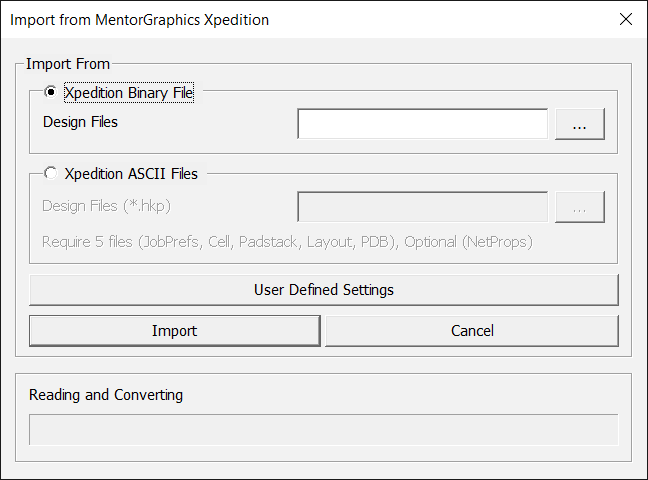

- Beta release of Siemens Xpedition importer directly from its binary data by

using the API.

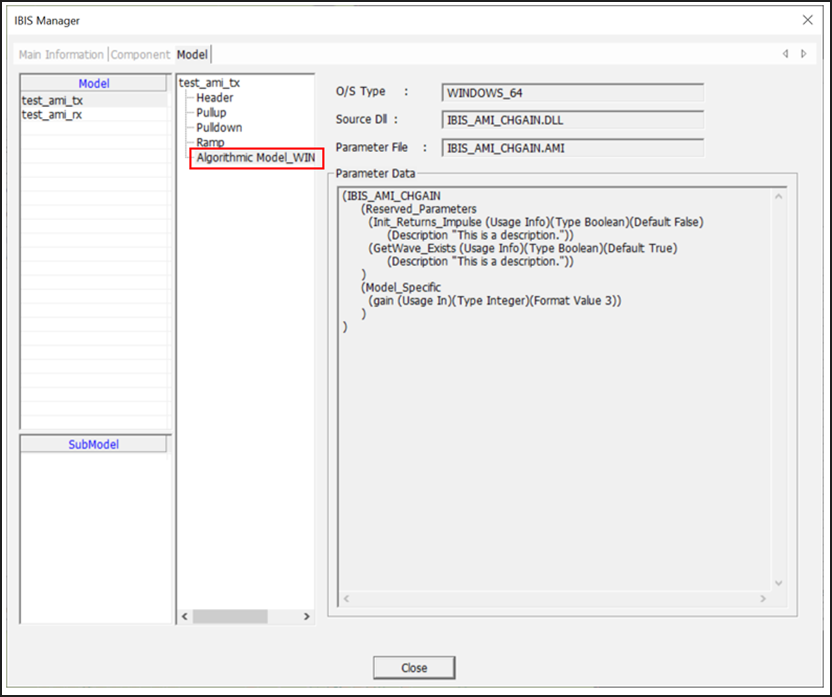

- Added to support the IBIS-AMI model for SerDes analysis in SI.

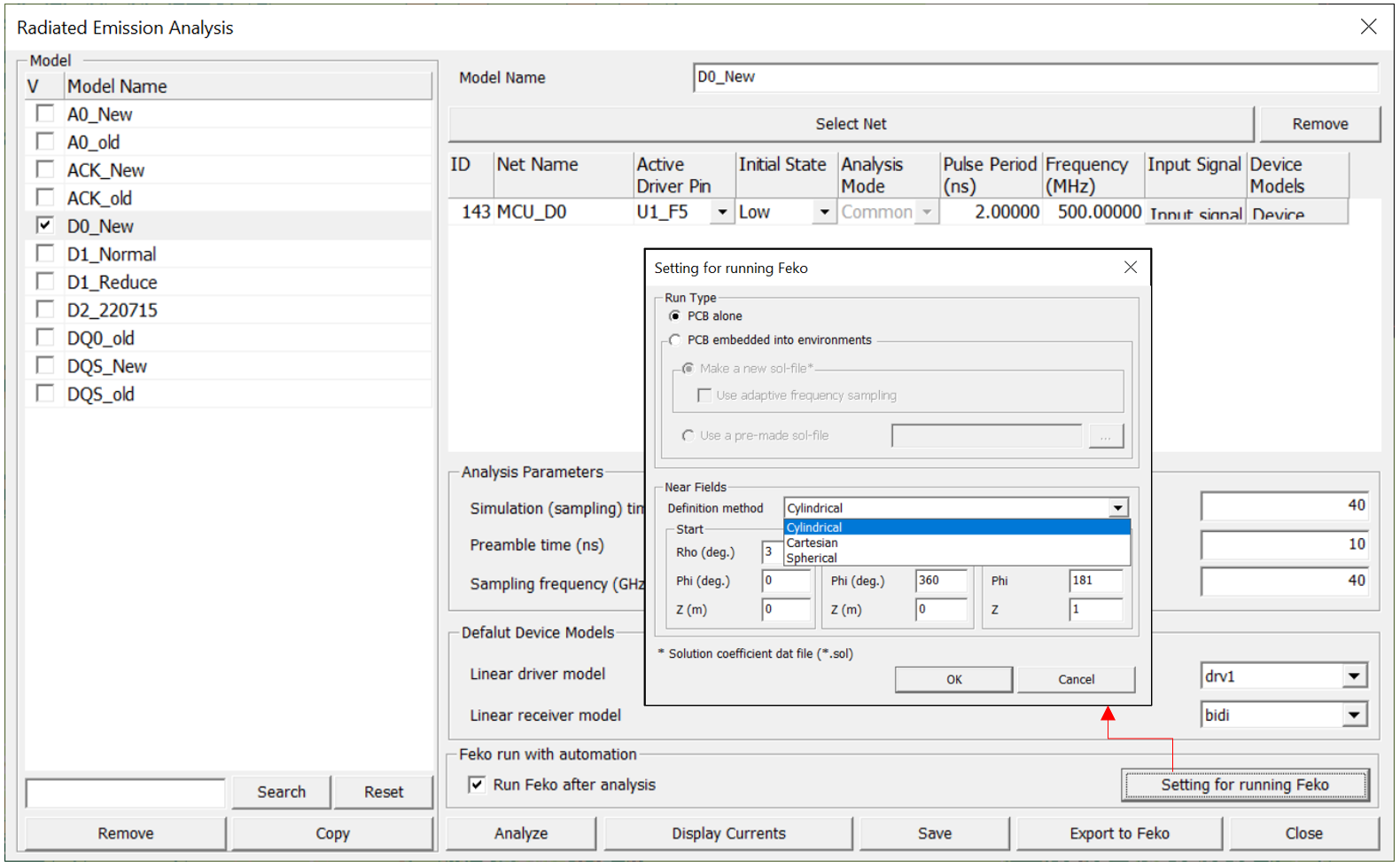

- Modified the Radiated Emission analysis of the SI to

process automatically using the Feko Lua script. The process of performing

radiated emission analysis in PollEx and using the

result to perform Near Field Radiation analysis in Feko is automatically

performed.

New Features

- PollEx Modeler

- PCB

- Added a function to import and export Power Information (such as voltage, current, and target impedance) in Excel format in the Electrical & Thermal Properties dialog of Parts. This feature enables users to set manually power information without an IBIS model.

- PollEx Verification

- Logic DFE

- Added a function to set Net Group using Net Property information.

- PollEx Analysis

- SI

- Added a function in the Net Topology to calculate and display capacitance for each segment of the net. This function can be used as intermediate data when calculating the total capacitance of the net or implementing the radiated emission function.

Enhancements

- PollEx Modeler

- PCB

- Modified the Board Information to display the correct PDBB saved version.

- PollEx Verification

-

- Enhanced the local web help to open the DFM, DFA, DFE, DFE+, and Logic DFE items you are viewing when pressing the F1 key.

- Modified the Component Classification Setting in DFM and DFA to display used checking item names when deleting groups.

- PollEx Analysis

- PI

- Modified the Parts dialog in the PI Analyzer (PIA) to display component simulation model information such as Model Type, Model File, and Model Name.

- Enhanced to generate anti-pad automatically when VIA is added in the PI Analyzer (PIA).

- Enhanced visibility by adding and displaying port information to the IR-Drop analysis result image.

- PollEx UPE

-

- Enhanced the STEP file importer to recognize the colors of the 3D shapes.

- Removed WRAPAROUND lead type from the Package Lead Editor.

- PollEx Interface from ECAD

- Cadence Allegro

- Enhanced the Allegro importer speed.

Resolved Issues

- Consolidated the measure feature to the View menu in CAM.

- Fixed a bug in the merge feature of the PCB Redmark.

- Fixed a bug to support a new aperture file format (*.phl) created by the Zuken tool.

- Fixed a bug in the merge feature of the DFM point tool.

- Fixed a result display error in the Placement Keepout and Via Spacing2 items of DFM.

- Fixed a bug in the DFE result table in which Link to ECAD with Xpedition functions did not work.

- Fixed a bug in Logic DFE that in the process of calculating the voltage value in the Voltage Divider Logic, an error occurred depending on the Pin Type setting of the IC.

- Fixed an issue in PI where Bundled Spice model could not be used in passive components.

- Fixed a bug of not recognizing lowercase characters in the Spice model name of the passive component in PI.

- Modified the Solder Quantity Calculator to recognize the figure shapes drawn as DIMENSION type.