Test-Point Location Generator Tutorial

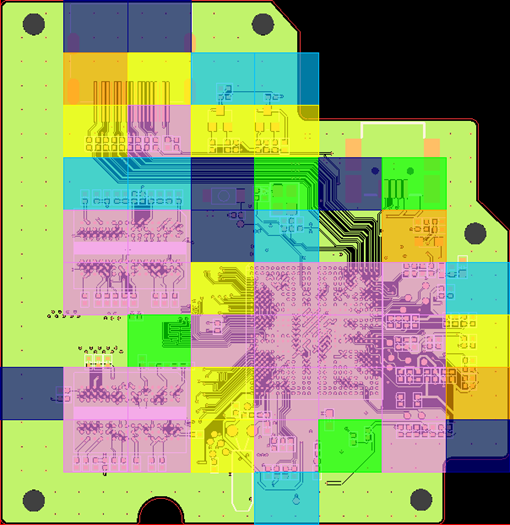

Test-Point Location Generator is a software for generating test points and extracting the location and data by referring to the design data.

Depending on the routing structure, this software provides versatile functions to generate test point locations. Use this software to load a netlist used and modified in manufacturing sites and to compare them with the original design data. Test-Point Location Generator is under the Manufacturer menu in PollEx PCB including three menus; Extract JIG Data, Result Review, and Verify Netlist.

- Launch PollEx PCB.

-

From the menu bar, click and open the

PollEx_MFG_Sample_T2_r<revision

number>.pdbb file from:

C:\ProgramData\altair\PollEx\<version>\Examples\MFG\.

Refer to the PCB for how to use the PollEx PCB viewer.

- From the menu bar, click .

-

From the menu bar, click .

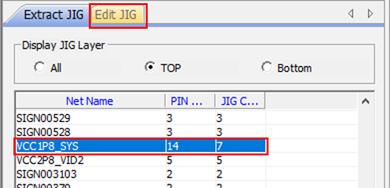

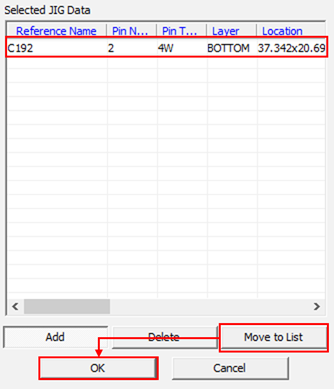

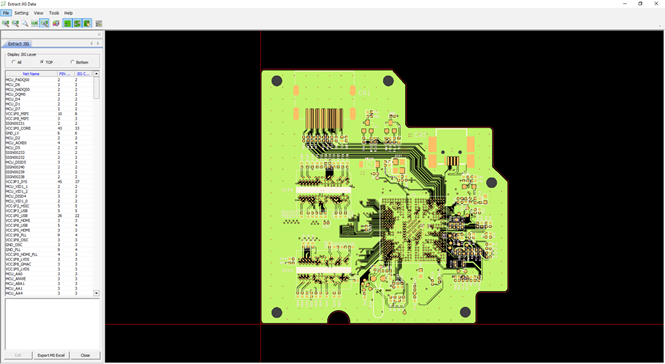

The extracted JIG data are displayed on the left-side of the Extract JIG Data dialog.

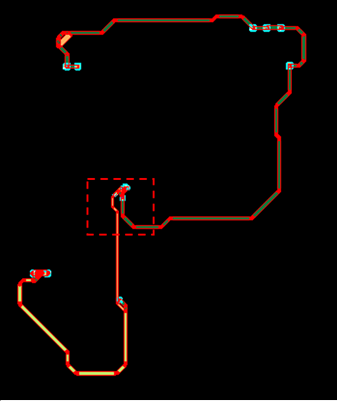

Figure 1.

-

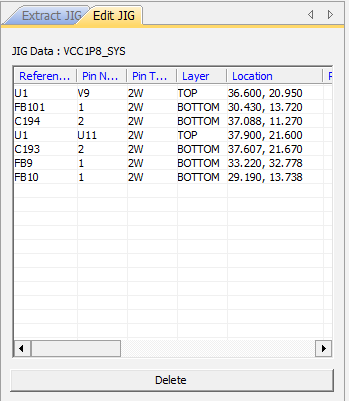

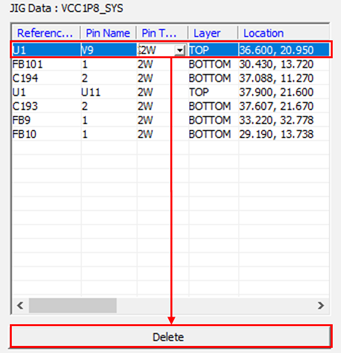

Edit JIG Data.

-

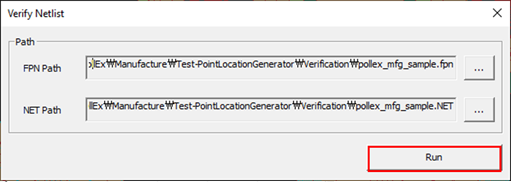

Verify Netlist.

-

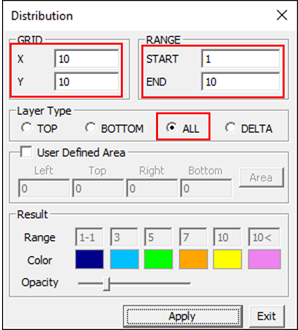

Define distribution.

-

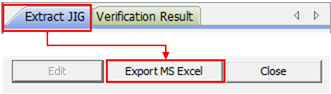

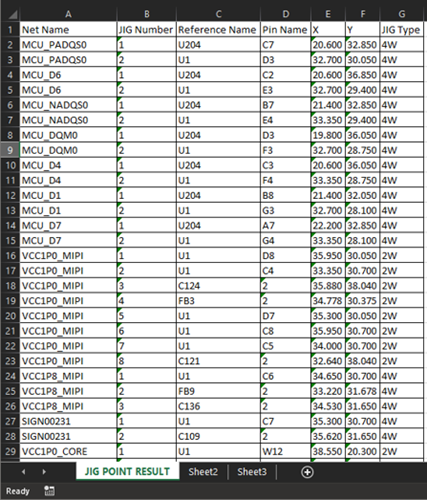

From the Extract JIG tab, click Export MS Excel to

export extract JIG data.

Figure 11.

Figure 12.

- From the menu bar, click .

-

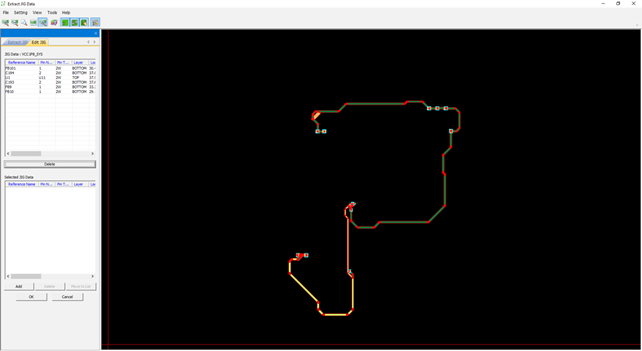

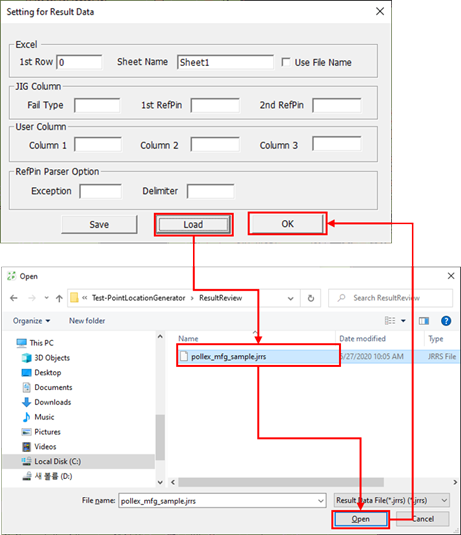

Set Result Data.

-

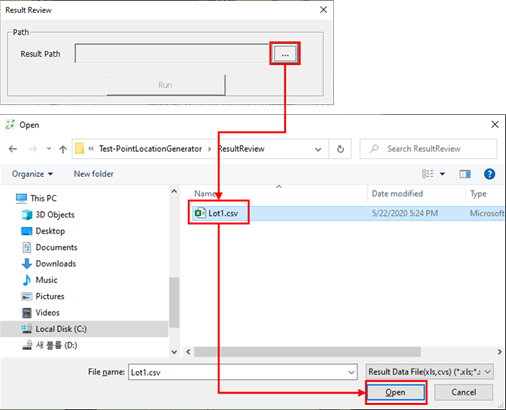

Open the Result Data.

-

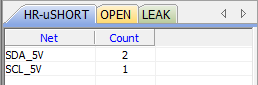

Open verify netlist.

This function is very similar to the function defined in step 6, but this provides the comparison including JIG pins data. This menu does not require to run Extract JIG Data before executing this menu.