DiscreteDelay

This block, when activated, outputs its state then stores its input in its state. When activated at a fixed rate, the block realizes a single-step delay represented by z-inverse in the Z transform domain.

![]()

Library

Activate/Dynamical

Description

The DiscreteDelay block delays its input by the specified sample period. The block is equivalent to the 1/z discrete-time operator. The block accepts one input and generates one output. The input and output can be either both scalar or vector. If the input is a vector, all elements of the vector are delayed by the same sample period.

This block implements a unit delay on discrete signal. To delay by arbitrary number of samples, ShiftRegister block can be used instead.

When activated at a fixed rate, this block realizes a single-step delay represented by z-inverse in the Z transform domain.

This block supports all data types that Activate supports. The output inherits its data type from the "initial condition".

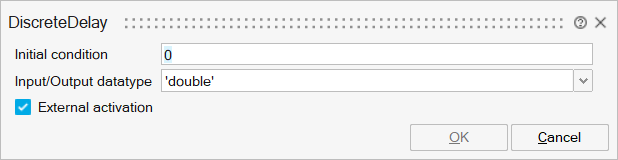

Parameters

| Name | Label | Description | Data Type | Valid Values |

|---|---|---|---|---|

init_cond | Initial condition | The output of the simulation for the first sampling period, during which the output of the DiscreteDelay block is otherwise undefined. | Matrix | |

typ | Input/Output datatype | Specifies the data type of the input and output. | String | 'double' |

externalActivation | External activation | This parameter defines if the block receives an external activation or inherits its activation through its regular input ports. When External Activation is used, an activation port is added to the block. | Number | 0 |

Ports

| Name | Type | Description | IO Type | Number |

|---|---|---|---|---|

Port 1 | explicit | output | 1 | |

Port 2 | explicit | input | 1 | |

Port 3 | activation | input | externalActivation |

Advanced Properties

| Name | Value | Description |

|---|---|---|

always active | no | |

direct-feedthrough | no | |

zero-crossing | no | |

mode | no | |

continuous-time state | no | |

discrete-time state | yes |