Package Modelica.Electrical.Digital.Memories

Package Modelica.Electrical.Digital.MemoriesIcon for standard packages

Package Modelica.Electrical.Digital.Memories

Package Modelica.Electrical.Digital.Memories

Standard package icon.

Extends from Modelica.Icons.Package (Icon for standard packages).

| Name | Description |

|---|---|

DLATRAM | Level sensitive Random Access Memory |

DLATROM | Level sensitive Read Only Memory |

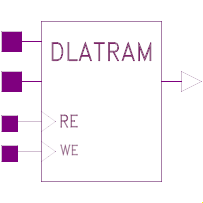

Model Modelica.Electrical.Digital.Memories.DLATRAM

Model Modelica.Electrical.Digital.Memories.DLATRAM

Description in VHDL is given by http://www.cs.sfu.ca/~ggbaker/reference/std_logic/src/std_logic_entities.vhd

Truth Table for high active read enable RE:

| RE | Addr | DataOut |

| 0 | * | Z over all |

| 1 | no X in Addr | DataOut=m(Addr) |

| 1 | X in Addr | X over all |

| X | * | X over all |

Truth Table for high active write enable WE:

| WE | Addr | Memory |

| 0 | * | no write |

| 1 | no X in Addr | m(Addr)=DataIn |

| 1 | X in Addr | no write |

| X | no X in Addr | m(Addr)=X over all |

| X | X in Addr | no write |

* = do not care 0 = L.'0' or L.'L' 1 = L.'1' or L.'H' X = L.'X' or L.'W' or L.'Z' or L.'-' or L.'U' Z = L.'Z'

Simultaneous read/write operations are allowed. Firstly Write is carried out, then Read.

Extends from Modelica.Electrical.Digital.Interfaces.MemoryBase (Base model for memory elements).

| Type | Name | Default | Description |

|---|---|---|---|

Time | tHL | 0 | High->Low delay |

Time | tLH | 0 | Low->High delay |

Strength | strength | S.'S_X01' | Output strength |

Integer | n_addr | 2 | Addr width |

Integer | n_data | 2 | Data width |

String | fileName | Modelica.Utilities.Files.loadResource("modelica://Modelica/Resources/Data/Electrical/Digital/Memory_Matrix.txt") | File where matrix for memory is stored |

| Type | Name | Description |

|---|---|---|

input DigitalInput | RE | Read enable |

input DigitalInput | addr[n_addr] | Address |

output DigitalOutput | dataOut[n_data] | Data output |

input DigitalInput | WE | Write enable |

input DigitalInput | dataIn[n_data] | Data input |

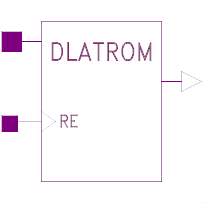

Model Modelica.Electrical.Digital.Memories.DLATROM

Model Modelica.Electrical.Digital.Memories.DLATROM

Description in VHDL is given by http://www.cs.sfu.ca/~ggbaker/reference/std_logic/src/std_logic_entities.vhd

Truth Table for high active read enable RE:

| RE | Addr | DataOut |

| 0 | * | Z over all |

| 1 | no X in Addr | DataOut=m(Addr) |

| 1 | X in Addr | X over all |

| X | * | X over all |

* = do not care 0 = L.'0' or L.'L' 1 = L.'1' or L.'H' X = L.'X' or L.'W' or L.'Z' or L.'-' or L.'U' Z = L.'Z'

Extends from Modelica.Electrical.Digital.Interfaces.MemoryBase (Base model for memory elements).

| Type | Name | Default | Description |

|---|---|---|---|

Time | tHL | 0 | High->Low delay |

Time | tLH | 0 | Low->High delay |

Strength | strength | S.'S_X01' | Output strength |

Integer | n_addr | 2 | Addr width |

Integer | n_data | 2 | Data width |

String | fileName | Modelica.Utilities.Files.loadResource("modelica://Modelica/Resources/Data/Electrical/Digital/Memory_Matrix.txt") | File where matrix for memory is stored |

| Type | Name | Description |

|---|---|---|

input DigitalInput | RE | Read enable |

input DigitalInput | addr[n_addr] | Address |

output DigitalOutput | dataOut[n_data] | Data output |