Target Category: STM32

Target Sub-Category: PWM

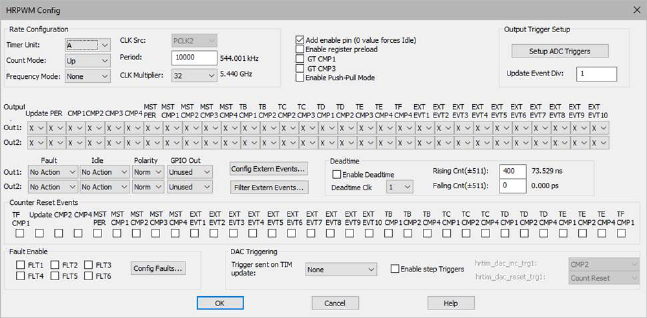

Description: The HRPWM block is based on the HRTIM unit found on the G4, F3, and H7 parts. The core clock for the timer unit has a multiplier of up to 32x the system clock. For the 170 MHz G4x4 parts, it gives an effective base clock of 5.44 GHz. This means that a period of 5440 gives a PWM carrier frequency of 1 MHz. There are six separate PWM units, each with its own counter, four compare registers, and two outputs that can be used in complementary mode or independent mode. Deadtime can be positive or negative and set in increments of 184 picoseconds.

Intricate phase waveforms can be developed using 32 different HRTIM counter reset signals including signals from all the other timers.

For more information, see the STMicroelectronics documentation for the device you are using.

Add enable pin: Adds an input pin to the block. A value of 0 puts the PWM in idle mode; a value of 1 lets the PWM run normally.

Counter Reset Events: Select events to reset the specified timer unit’s counter to 0. You can select more than one event.

Deadtime Clk Prescale: Specifies the clock divisor for the deadtime. The divisor divides the timer clock to obtain a deadtime clock.

Enable Deadtime: Enables deadtime. Once activated, you can specify the falling and rising values. Both falling and rising can be negative values.

Falling Cnt: Specifies the falling value. The value displayed to the right of the text box is the length of the deadtime in terms of timer ticks.

Rising Cnt: Specifies the rising value. The value displayed to the right of the text box is the length of the deadtime in terms of timer ticks.

Enable set Triggers: Enables step and reset triggers to be sent to the DAC for sawtooth waveform generation. The step trigger generates a number of requests for DAC value increments or decrements. If the step trigger selection is CMP2, then the value presented on the CMP2 input pin to the HRPWM block is snapped at the PWM reset time. After a compare match occurs (which generates a step trigger), the original snapped CMP2 value is added to the current CMP2 value causing a number of step triggers to be generated between reset and period. The total number of step triggers per PWM cycle is equal to the period divided by the orignal snapped CMP2 value. The reset trigger is sent when the count rolls back to zero after reaching the period.

Trigger sent on TIM update: Generates trigger for the DAC random noise and triangle waveform generation.

Enable push-pull mode: Enables push-pull mode.

Enable register preload: When the preload mode is enabled, accessed registers are shadow registers. Their content is transferred into the active register after an update event.

FLT1-6: Selects the fault source. Select as many as are necessary.

Config Faults: Opens HRPWM Fault Config dialog to configure the six system-wide HRTIM faults and blanking window.

GT CMP1, GT CMP2: Enables one of the following:

•An early turn-off of the output if the new compare value is below the current counter value and the current compare value is above the counter, at the time the new value is written.

•An early turn-on of the output, re-enabling the output if the new compare value is above the counter value and the current compare value is above the counter, at the time the new value is written.

The output signal is left unchanged when the new compare value and current compare value are both below the counter.

This feature is only available for CMP1 or CMP3 RESET events. The preload mechanism is inactive for a compare register when the corresponding GTCMPx bit is set.

Out 1: Selects events to set PWM output high (1) or low (0) during the course of the PWM count-to-period.

•Update: Match to counter.

•PER: Match to period.

•CMP1-4: Match to compare 1 – 4.

•MST PER: Match to master period.

•Update: Match to counter.

•TxCMP1-4: Match to external timer.

•EXT EVT1-10: Match to external event.

•Fault: If a fault occurs, drive to the selection.

•Idle: If both fault and idle modes are active, idle mode takes precedence. If input to the enable pin is 0, block outputs are in idle mode.

•Polarity: Allows for inversion of the output waveform.

•GPIO Out: Selects the output pin for the PWM signal.

Out 2: Selects events to set PWM output high (1) or low (0) during the course of the PWM count-to-period.

•Update: Match to counter.

•PER: Match to period.

•CMP1-4: Match to compare 1 – 4.

•MST PER: Match to master period.

•Update: Match to counter.

•TxCMP1-4: Match to external timer.

•EXT EVT1-10: Match to external event.

•Fault: If a fault occurs, drive to the selection.

•Idle: If both fault and idle modes are active, idle mode takes precedence. If input to the enable pin is 0, block outputs are in idle mode.

•Polarity: Allows for inversion of the output waveform.

•GPIO Out: Selects the output pin for the PWM signal.

Config Extern Events: Opens the Config Extern Events dialog to configure external events.

Filter Extern Events: Opens the Filter Extern Events dialog to filter external events.

Setup ADC Triggers: Opens the ADC SOC dialog to set up the ADC triggers.

Update Event Div: Divisor for the update event used to send update event triggers. For example, if you enter 1, the trigger is sent out for every update event; if you enter 2, it sends out every other update event, and so on. An update event occurs when you get a counter overflow or underflow.

CLK Src: Specifies the clock source. If there is a choice, it will be in the dropdown menu.

CLK Multiplier: Scales the timer source to a slower or faster rate. Can be any value between 0.25 and 32.

Count Mode: Selects the counter behavior.

Period: Specifies the duration of a PWM waveform in units of timer ticks. In conjunction with the system clock selected for the timer, the timer Multiplier and Count Mode, determines the frequency of the PWM waveform. For example, if the base clock rate is 170 MHz and Multiplier is 32 and the Count Mode is Up, the effective clock rate is 5.44 GHz. The frequency appears to the right of the Period.

Timer Unit: Specifies the timer unit to be configured.