NXFERGATE

Transfergate with enable active high

![]()

Library

Modelica/Electrical/Digital/Tristates

Description

Description in VHDL is given by http://www.cs.sfu.ca/~ggbaker/reference/std_logic/src/std_logic_entities.vhd

Truth Table

| DataIn | Enable | DataOut |

| * | U | U |

| * | X | UX |

| * | 0 | Z |

| * | 1 | DataIn |

| * | Z | UX |

| * | W | UX |

| * | L | Z |

| * | H | DataIn |

| * | - | UX |

UX: if dataIn == U then U else X

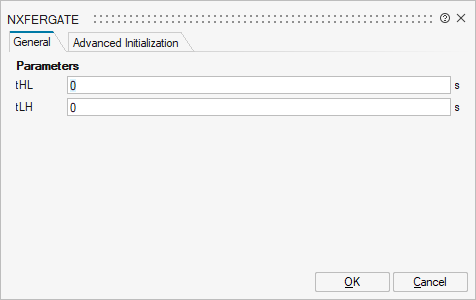

Parameters

| Name | Label | Description | Data Type | Valid Values |

|---|---|---|---|---|

mo_tHL | tHL | High->Low delay | Scalar | |

mo_tLH | tLH | Low->High delay | Scalar |

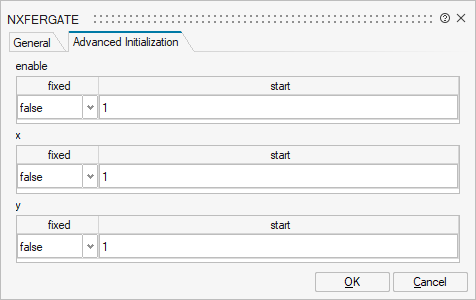

| Name | Label | Description | Data Type | Valid Values |

|---|---|---|---|---|

mo_enable | enable | enable | Structure | |

mo_enable/fixed | fixed | Cell of scalars | true | |

mo_enable/start | start | Cell of scalars | ||

mo_x | x | x | Structure | |

mo_x/fixed | fixed | Cell of scalars | true | |

mo_x/start | start | Cell of scalars | ||

mo_y | y | y | Structure | |

mo_y/fixed | fixed | Cell of scalars | true | |

mo_y/start | start | Cell of scalars |

Ports

| Name | Type | Description | IO Type | Number |

|---|---|---|---|---|

enable | implicit | input | 1 | |

x | implicit | input | 2 | |

y | implicit | output | 1 |