DA_Converter

Simple digital to analog converter

![]()

Library

Modelica/Electrical/Analog/Ideal

Description

Simple digital to analog converter with a variable input signal width of N bits. The input signal is an N-vector of type Logic (9-valued logic according to IEEE 1164 STD_ULOGIC). The output voltage of value y is generated by an ideal voltage source. The output can only change if the trigger signal trig of type Logic changes to '1' (forced or weak). In this case, the output voltage is calculated in the following way:

N

y = SUM ( x[i]*2^(i-1) )*Vref/(2^N-1),

i=1

where x[i], i=1,...,N is 1 or 0. and Vref is the reference value. Therefore, the first bit in the input vector x[1] is the least significant one (LSB) and x[N] is the most significant bit (MSB).

This is an abstract model of a DAC. Hence, it can not cover the dynamic behaviour of the converter. Therefore the output will change instantaneously when the trigger signal rises.

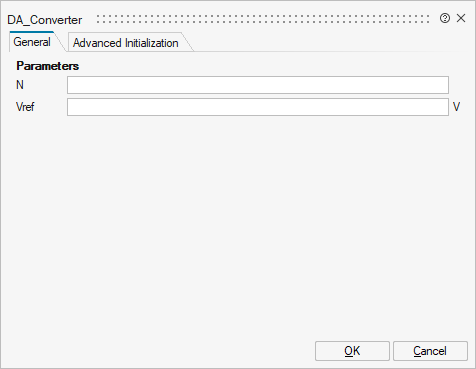

Parameters

| Name | Label | Description | Data Type | Valid Values |

|---|---|---|---|---|

mo_N | N | Resolution - input signal width | Scalar | |

mo_Vref | Vref | Reference voltage | Scalar |

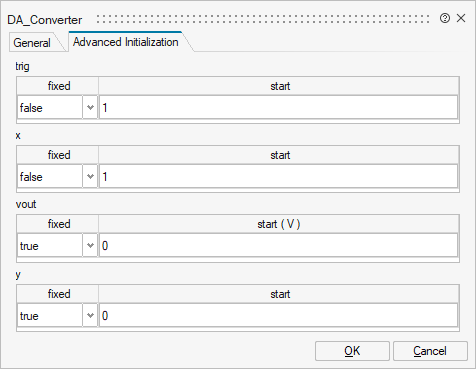

| Name | Label | Description | Data Type | Valid Values |

|---|---|---|---|---|

mo_trig | trig | trig | Structure | |

mo_trig/fixed | fixed | Cell of scalars | true | |

mo_trig/start | start | Cell of scalars | ||

mo_x | x | x | Structure | |

mo_x/fixed | fixed | Cell of vectors | true | |

mo_x/start | start | Cell of vectors | ||

mo_vout | vout | vout | Structure | |

mo_vout/fixed | fixed | Cell of scalars | true | |

mo_vout/start | start | Cell of scalars | ||

mo_y | y | y | Structure | |

mo_y/fixed | fixed | Cell of scalars | true | |

mo_y/start | start | Cell of scalars |

Ports

| Name | Type | Description | IO Type | Number |

|---|---|---|---|---|

trig | implicit | Trigger input | input | 1 |

x | implicit | Digital input | input | 2 |

p | implicit | Positive electrical pin (output) | input | 3 |

n | implicit | Negative electrical pin (output) | output | 1 |