NMOS

Simple MOS Transistor

![]()

Library

Modelica/Electrical/Analog/Semiconductors

Description

The NMOS model is a simple model of a n-channel metal-oxide semiconductor FET. It differs slightly from the device used in the SPICE simulator. For more details please care for H. Spiro.

The model does not consider capacitances. A high drain-source resistance RDS

is included to avoid numerical difficulties.

Please note:

In case of useHeatPort=true the temperature dependence of the electrical

behavior is not modelled yet. The parameters are not temperature dependent.

W L Beta Vt K2 K5 DW DL m m A/V^2 V - - m m 12.e-6 4.e-6 0.062e-3 -4.5 0.24 0.61 -1.2e-6 -0.9e-6 depletion 60.e-6 3.e-6 0.048e-3 0.1 0.08 0.68 -1.2e-6 -0.9e-6 enhancement 12.e-6 4.e-6 0.0625e-3 -0.8 0.21 0.78 -1.2e-6 -0.9e-6 zero 50.e-6 8.e-6 0.0299e-3 0.24 1.144 0.7311 -5.4e-6 -4.e-6 20.e-6 6.e-6 0.041e-3 0.8 1.144 0.7311 -2.5e-6 -1.5e-6 30.e-6 9.e-6 0.025e-3 -4.0 0.861 0.878 -3.4e-6 -1.74e-6 30.e-6 5.e-6 0.031e-3 0.6 1.5 0.72 0 -3.9e-6 50.e-6 6.e-6 0.0414e-3 -3.8 0.34 0.8 -1.6e-6 -2.e-6 depletion 50.e-6 5.e-6 0.03e-3 0.37 0.23 0.86 -1.6e-6 -2.e-6 enhancement 50.e-6 6.e-6 0.038e-3 -0.9 0.23 0.707 -1.6e-6 -2.e-6 zero 20.e-6 4.e-6 0.06776e-3 0.5409 0.065 0.71 -0.8e-6 -0.2e-6 20.e-6 4.e-6 0.06505e-3 0.6209 0.065 0.71 -0.8e-6 -0.2e-6 20.e-6 4.e-6 0.05365e-3 0.6909 0.03 0.8 -0.3e-6 -0.2e-6 20.e-6 4.e-6 0.05365e-3 0.4909 0.03 0.8 -0.3e-6 -0.2e-6 12.e-6 4.e-6 0.023e-3 -4.5 0.29 0.6 0 0 depletion 60.e-6 3.e-6 0.022e-3 0.1 0.11 0.65 0 0 enhancement 12.e-6 4.e-6 0.038e-3 -0.8 0.33 0.6 0 0 zero 20.e-6 6.e-6 0.022e-3 0.8 1 0.66 0 0

- References:

- Spiro, H.: Simulation integrierter Schaltungen. R. Oldenbourg Verlag Muenchen Wien 1990.

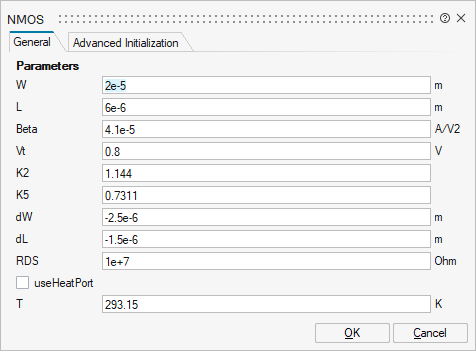

Parameters

| Name | Label | Description | Data Type | Valid Values |

|---|---|---|---|---|

mo_W | W | Width | Scalar | |

mo_L | L | Length | Scalar | |

mo_Beta | Beta | Transconductance parameter | Scalar | |

mo_Vt | Vt | Zero bias threshold voltage | Scalar | |

mo_K2 | K2 | Bulk threshold parameter | Scalar | |

mo_K5 | K5 | Reduction of pinch-off region | Scalar | |

mo_dW | dW | Narrowing of channel | Scalar | |

mo_dL | dL | Shortening of channel | Scalar | |

mo_RDS | RDS | Drain-Source-Resistance | Scalar | |

mo_useHeatPort | useHeatPort | =true, if heatPort is enabled | Number | 0 |

mo_T | T | Fixed device temperature if useHeatPort = false | Scalar |

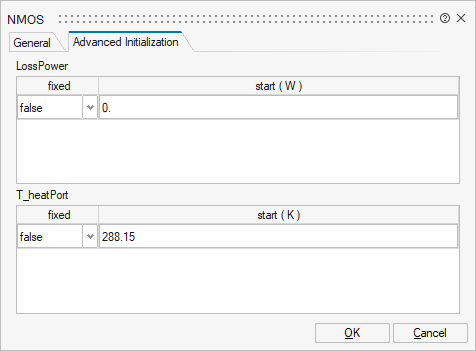

| Name | Label | Description | Data Type | Valid Values |

|---|---|---|---|---|

mo_LossPower | LossPower | LossPower | Structure | |

mo_LossPower/fixed | fixed | Cell of scalars | true | |

mo_LossPower/start | start | Cell of scalars | ||

mo_T_heatPort | T_heatPort | T_heatPort | Structure | |

mo_T_heatPort/fixed | fixed | Cell of scalars | true | |

mo_T_heatPort/start | start | Cell of scalars |

Ports

| Name | Type | Description | IO Type | Number |

|---|---|---|---|---|

D | implicit | Drain | input | 1 |

G | implicit | Gate | input | 2 |

S | implicit | Source | input | 3 |

B | implicit | Bulk | input | 4 |

Port 5 | implicit | Conditional heat port | input | mo_useHeatPort |