Target Category: Delfino, Piccolo

Target Sub-Category: ADC

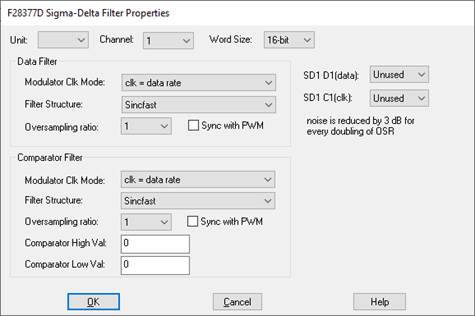

Description: The Sigma Delta Filter Module block is a general-purpose decoder of analog signals from digital bit streams.

Additional Information: Texas Instruments TI 28377D Technical Reference Manual.

Comparator Low Val: Indicates the lower threshold for the signal. If the signal crosses the lower threshold, corresponding bits will be set in the Interrupt Flag (SDIFLG) register.

Comparator High Val: Indicates the upper threshold for the signal. If the signal crosses the upper threshold, corresponding bits will be set in the Interrupt Flag (SDIFLG) register.

Filter Structure: Indicates the filter structure to be used.

Modulator Clk Mode: Lets you choose the speed of the modulator clock. If you are doing Manchester encoded data, select No Clk.

Oversampling Ratio: Lets you choose between 1 and 32. Higher values yield more higher analog signal precision, but slower overall sampling rates.

Sync with PWM: Synchronizes the oversampling ratio with the PWM.

Channel: Specifies the analog input channel.

Filter Structure: Indicates the filter structure to be used.

Modulator Clk Mode: Lets you choose the speed of the modulator clock. If you are doing Manchester encoded data, select No Clk.

Oversampling Ratio: Lets you choose between 1 and 256. Higher values yield more higher analog signal precision, but slower overall sampling rates.

Sync with PWM: Synchronizes the oversampling ratio with the PWM.

SD1 C1 (clk): Chooses the pin that the clock comes in on.

SD1 D1(data): Chooses the pin that the data comes in on.

Unit: Specifies the unit number.

Word Size: Selects the word size of the output.